2017 EMC設計技術実践講座

主催:エレクトロニクス実装学会 低ノイズ実装研究会

主催者より

皆さんは、多層基板を設計する上で層構成に悩んだことはありませんか?また、4層基板で電源は3層にまとめますか、それともこだわりませんか。多電源の場合、電源は面でしょうか、配線でも良いとお考えでしょうか。さらに表面層はグランドベタで覆った方が良いでしょうか、パスコンはお守りとして出来るだけ多い方が良いでしょうか。これらはいずれも過去のセミナーで出た問題です。

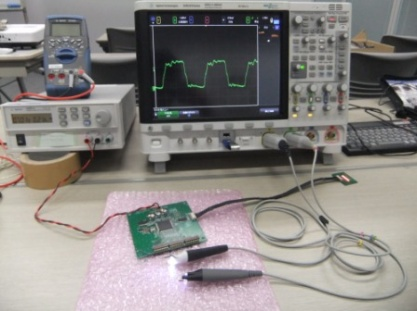

本講座では、いくつかのグループに分かれていただき、モデル回路をベースに基板の設計とシミュレーションを行い、実際に基板を作って測定、評価までをグループ単位で行います。同じ回路でも層構成、基板の設計法(上記で述べた問題点など)の違いによってノイズの出方が大きく変わってしまうことを実際に体感していただきます。

本講座の特徴は、受講者全員にCAD(CADVANCE:図研)を使って基板設計をしていただくこと、その設計の良し悪しをSIシミュレータ(SignalAdviser-SI:富士通)、EMIルールチェッカ(DEMITASNX:NEC)を使って把握していただくこと、実際に基板を作って評価してみること(グループ結果を比較し、どの設計法がノイズ低減に役立つかを客観的に把握できる)、さらに本講座では、今までの講座で対策まで行いたいという多くのご要望より、電波暗室に基板を持ち込み、皆さまに対策を行っていただくこと、その結果をもとに再設計→再測定→評価 までを行うことにしました。

上記のCAD, シミュレータは、講座期間中、皆さんのPCにインストールしていただき、自由にお使いいただけます。シミュレータを身近に感じていただくこと、シミュレータの結果から次の策を読みとる能力を養っていただきたいという主催者の願いから、各ベンダー様に協力いただくことにしております。

座学、もの作り、討議など、さまざまな企画を通じて、どなたにも無理なくノイズの特質をご理解いただくことができます。「学会の講座はレベルが高くて難しい」という常識をくつがえそうという狙いもこの企画には含まれています。やる気さえあれば、どなたにも満足いただける講座であろうと思います。

昨年まで過去7回、同講座を開催いたしましたが、ご参加頂いた方々より大変好評をいただいております。

どうぞ積極的にご参加いただきますよう、よろしくお願いいたします。

詳細

| 実施期間 | 2017年5月12日から2018年1月26日まで(全12回) | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 会 場 |

回路会館 地下1階会議室 JR中央線西荻窪駅下車徒歩約7分 〒167-0042 東京都杉並区西荻北3-12-2 TEL.03-5310-2010 アクセス |

||||||||||||||||||||||||||||||

| 対象者 | プリント基板を扱う技術者、またはそれに準ずる業務に携わられている方 | ||||||||||||||||||||||||||||||

| 参 加 費 |

* この機にエレクトロニクス実装学会に入会していただきますと,会員価格での参加が可能です。非会員の方はぜひご検討下さい。 | ||||||||||||||||||||||||||||||

| 定 員 | 60名(先着申込順 定員になり次第,締め切らさせていただきます。受付締め切りの場合は学会ホームページ上でお知らせします) | ||||||||||||||||||||||||||||||

| 申込方法 |

下記申込書の内容をEメールでお送りください。 宛先は e-kenkyukai(at)jiep.or.jp です。 ※メール送信時は(at)をアットマークにしてください。 *ご注意 |

||||||||||||||||||||||||||||||

| スケジュール ※時間は全日10:00~17:30 |

* 第2回講座より,PCを用いた実演に入ります。各自ノートPCをご用意願います。詳しくは以下の受講に関する注意事項を事前にお読みください。 |

||||||||||||||||||||||||||||||

| お申し込み先 |

(一社)エレクトロニクス実装学会 〒167-0042 東京都杉並区西荻北3-12-2 TEL 03-5310-2010 FAX 03-5310-2011 メール e-kenkyukai(at)jiep.or.jp です。 ※メール送信時は(at)をアットマークにしてください。 |

||||||||||||||||||||||||||||||

参加申込書

宛先:

e-kenkyukai(at)jiep.or.jp

※メール送信時は(at)をアットマークにしてください。

2017 EMC設計技術実践講座

参加申込書(2017/5~2018/1)

会員種別:

( )正会員[No. ] ( )賛助会員[No. ]

( )今回入会手続き済 ( )今回入会予定

( )非会員

氏名:

フリガナ:

性別:

年齢:

会社名:

所属:

郵便番号:

住所:

電話番号:

E-Mail:

受講者様の主な業務内容(複数選択可):

( )デジタル回路設計 ( )アナログ回路設計

( )パターン設計 ( )計測技術者

( )EMC専門家 ( )研究者

( )その他[ ]

お問い合わせ先

【講座の内容に関すること】

低ノイズ実装研究会主査までご連絡ください。【学会入会に関すること】

エレクトロニクス実装学会 事務局

メールアドレス: info(at)jiep.or.jp

※メール送信時に(at)をアットマーク@に変更ください。